Alex. Eng. J., Alex. Univ., Volum 27 No. 2, pp. 55-68 (1988)

# THE DESIGN OF AN ANALOG BY DIGITAL MULTIPLIER FOR ELECTROCARDIOGRAM SIGNAL PROCESSING

M.R.M. Rizk, A. Khalifa and A.A. Abo Ouf Elect. Eng. Dept., Alexandria University

# ABSTRACT

An electronic circuit is designed for Electrocardiogram (ECG) signal-processing in which the ECG signal-in analog form- is multiplied by a digital factor (time independent).

The circuit is based on the idea of controlling the gain of an operational amplifier by a digital signal. The circuit is designed to multiply an ECG analog varying from -100 mV to +100 mV by a digital factor varying from -100 to + 100.

Experimental results show that for the specified input range the maximum error is 0.5 % and the multiplication is frequency indpendent up to 100 KHz.

Alexandria Engineering Journal

## INTRODUCTION

Several applications of microprocessors in ECG signal processing involves multiplication of the analog ECG signal by the microprocessor outputs which are usually digital numbers [1], [2]. There are the alternatives to perform this multiplication, namely to convert the digital number to an analog one and perform an anlog by analog multiplication, or to convert the analog ECG signal to a digital one and perform a digital by digital multiplication, or to perform a direct analog by digital multiplication.

The first two methods depend on the conversion of an analog signal to a digital one or vice versa. This makes the implementation of both circuits very complex and expensive. Also the conversion rate of the D/A or A/D limits the maximum input analog signal frequency. In our case, where real time multiplication is needed, very high speed D/A's or A/D's are required which makes the system even more complex and expensive. The conversion process itself, depending on the resolution of the D/A or A/D introduces errors that render inaccurate system.

As the third method does not involve any conversion, it is simpler, less expensive and more accurate. The aim of this work is to design a simple Analog by Digital Multiplier (ADM) to perform the multiplication of an analog signal by a digital factor in the real time and with convenient accuracy.

Alexandria Engineering Journal

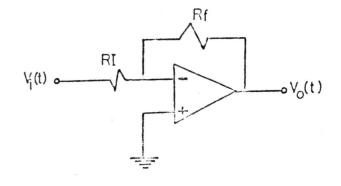

# Concep of Multiplication

The concept of the analogy be digital multiplier (ADM) is based on the idea of controlling, by digital signal, the gain of an operational amplifier. Figure 1 shows the circuit of an operational amplifier as an inverting amplifier. The relation between the magnitudes of the output and input voltage signals is as follows:

$$V_{c}(t) = R_{f}/R_{i} * V_{i}(t)$$

(1)

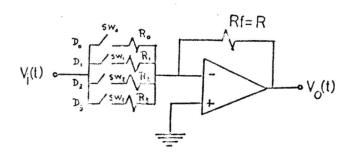

If we replace  $R_i$  by a set of parallel branches, each containing a resistance in series with a switch then the above relation becomes:

$$V_{0}(t) = R_{f}/R_{t} * V_{i}(t)$$

(2)

where  $R_t$  is the parallel combination of the resistance of those branches whose switches are on. Each switch is controlled by a digital input bit such that it is closed when the input bit is at logical l and opened if it is at logical 0. The resistance  $R_b$  in series with each switch is chosen such that:

$$R_b = R/N$$

(3)

where N is the weight of the digital input bit. For a 4-bit digital input word the circuit becomes as that shown in Figure 2.

# Alexandria Engineering Journal

# Design of the Multiplier Basic Circuit

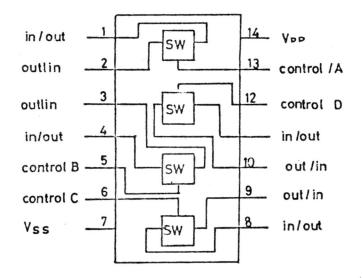

Consider the input digital word to be 8 bits wide, with the most significant bit reserved for the sign, the decimal equivalent of the digital input will vary from -128 to + 128, and the amplifier circuit of Figure 2 will be modified by introducing three more input branches. We assume the digital inputs to be TTL levels [3]. To implement the digitally controlled switches the CMCS Quad Bilateral switches (4066) [4] were used for the following features:

- (i) Low Cn-resistance (270 ohms at VDD 0 + 5V)

- (ii) Extremely low leakage current in the OFF state (0.1 nA).

- (iii) Frequency response, switch on up to 40 MHz.

- (iv) TTL compatability

- (v) Low current switch controls

- (vi) Analog signal range from (VSS-0.5) to (VDD + 0.5)

volts

- (vii) Low power consumption

(viii) Low price.

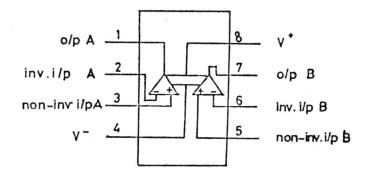

A schematic diagram of the 4066 switch package is shown in Figure 3.

The operational amplifier used in the circuit was chosen to be FET Dual operational amplifier (LF 353) for the following features:

- (i) Wide gain bandwidth (40 MHz)

- (ii) High input impedance  $(10^{12} \text{ ohms})$

Alexandria Engineering Journal

(iii) Low offset voltage (3 mV)

(iv) Low price.

A schematic diagram of the LF 353 package is shown in Fig 4.

The Most critical part of the circuit is the resistors. since the multilier accuracy depends upon the values of these resistances. The main factor determining the values of these resistances is the switch CN-resistance ( $R_{on} = 270$ ohms). The smallest resistance in the parallel branches is the one corresponding to the most significant bit which equals to

$$R_6 = R/64$$

(4)

Therefore for small error ,

R/64 >> 270 ohms (5)

If we take  $R_6$  to be 20 kilo-ohms, this gives sufficient accuracy. The values of the parallel resistors will thus be

| R              | = | 1.28 | mega-ohrs |

|----------------|---|------|-----------|

| R <sub>1</sub> | = | 640  | kilo-ohms |

| R <sub>2</sub> | = | 320  | kilo-ohms |

| R <sub>3</sub> | = | 160  | kilo-ohms |

| R <sub>4</sub> | = | 80   | kilo-ohms |

| R <sub>5</sub> | = | 40   | kilo-ohms |

| R              | = | 20   | kilo-ohms |

Alexandria Engineering Journal

(6)

It is not easy to have this wide range of precision resistors. To overcome this, trimmers in series with fixed resistors are used to give a precise overall resistance.

The feedback resistor Rf should be equal to R, which is 1.28 mega-ohms, for correct multiplication. If we set the maximum analog input to be 100 mV and the maximum digital input to be  $\pm$  10C, then the maximum output of the multiplier stage will be  $\pm$  10 V. But since the output of the multiplier stage is to drive the sign-bit stage, then Rf must be modified so as to bring down the maximum output of the multiplier stage to the levels adequate for the sign-bit stage.

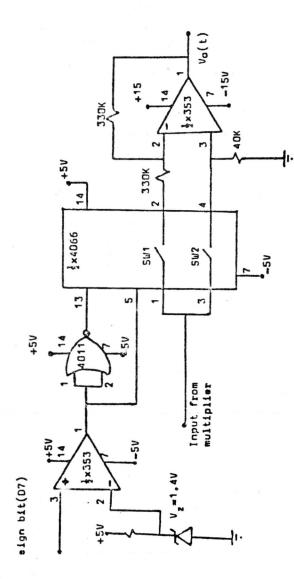

The circuit of Figure 5 is used to implement the sign-bit stage. It is such that when the sign-bit is at logical 0 then the digital word is taken to represent a positive number, and when the sign-bit is at logical 1 the number is a negative one. The cutput of the multiplier stage is fed to a 4066 switch. The input requirements of the switch is that the analog signal must be within VDD + 0.5 V and VSS - 0.5 V. Thus if Rf is halved, that is taken to be 640 kilo-ohms instead of 1.28 mega-ohms, then the output of the multiplier stage will be within  $\pm$  5 V.

For VDD = 5 V and VSS = -5 V this would be adequate since the 4066's input can thus vary from + 5.5 V to -5.5 V.

An operational amplifier is used at the input to interface between the TTL digital input and the CMOS switch. The CMOS NOR Gate (4011) is used as an inverter. The final

Alexandria Engineering Journal

# The Design Of An Analog By Digital Multiplier 61

operational amplifier was chosen to have a gain of 2 so as to compensate for the halving of Rf in the multiplier stage.

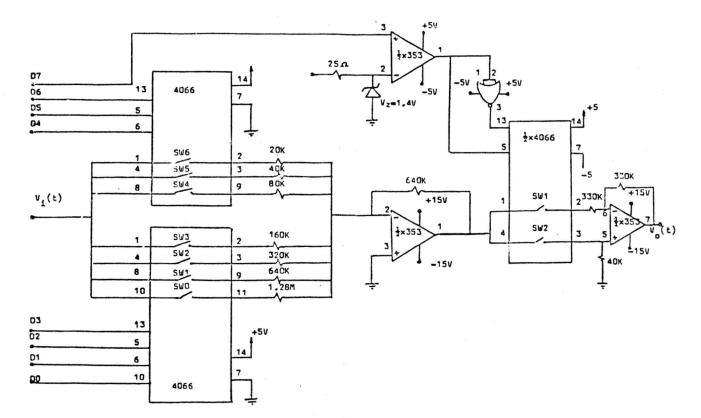

The final circuit of the analog by digital multiplier (ADM) is shown in Figure 6.

#### Experiments

The following experiments were made to check the accuracy resolution, and frequency response of the circuit: Experiment 1: The ADM was given a 100 mv input- the maximum design input-and the digital input was varied from 0 to 100 unit in steps of 1. The analog output was recorded.

Experiment 2: The ADM was given a sinusoidal input of 10C mV peak to peak and the digital input was set at 100. The frequency of the analog input signal was varied from d.c. to 1 MHz and the analog output was recorded.

# **RESULTS AND CONCLUSIONS**

In experiment 1 an offset of 3 mV to 9 mV was observed. When the maximum offset, corresponding to digital input 0, was compensated for, the output had an error not exceeding 0.5 % as in Table 1.

Assuming that the digital input varies from -100 to +10C as stated earlier, the required resolution is (1/100) or 1 %. Thus the maximum allowable error is  $\pm$  0.5 %. From the

# Alexandria Engineering Journal

# M.R.M. Rizk, A. Khalifa and A.A. Abo Ouf

results of experiment l we can see that the circuit satisfies this condition.

Experiment 2 yielded that the output was constant for input analog frequencies from d.c. up to 100 KHz. This shows that our ADM is frequency-independent in this range.

The analog by digital multiplier (ADM) presented has the following advantages:

- (i) Analog input level is between -loC mv and + loC mv with a frequency spectrum up to loC KHz.

- (ii) Digital input is 8-bit in sign magnitude representation with a decimal equivalent range of -100 to + 100.

- (iii) The output is analog and ranges between -10V and +10V.

- (iv) The maximum error is 0.5% of the maximum output voltage.

- (v) The multiplication is performed in the real time.

## REFERENCES

- [1] E.S. Fishman and Barber, "aimed electrocardiography: model studies using a heart consisting of 6 electrically isolated areas", Am. Heart J. 65: pp. 628-637, 1963.

- [2] A.A. Abo-ouf, "Microprocessor application in medical engineering", M.Sc. thesis, Fac. of Eng., Alexandria University, 1986.

Alexandria Engineering Journal

[3] Texas Instruments. TTL Data Book, 1981.[4] Motorola, CMOS Data Bock, 1982.

# ACKNOWLEDGMENT

The authors wish to thank Prof. Dr. M.M. Shabana for his interesting discussions and stimulating ideas.

Alexandria Engineering Journal

| Theor.<br>o/p                                                                                          | Exp.<br>o/p                                                                                                  | Error%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Theor.<br>o/p                                    | Ехр.<br>о/р                                             | Er |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------------|----|

| 012345678911123456789012345678901234567890123456789012345678901234567890123456789012345678901234567890 | $\begin{array}{c} 0.999643218554219821087054108754010875441076532198210877777777777777777777777777777777777$ | $\begin{array}{c} 0. \\ 0.02 \\ 0.03 \\ 0.04 \\ 0.067 \\ 0.088 \\ 0.114 \\ 0.112 \\ 10.121 \\ 0.222 \\ 233399 \\ 0.33399 \\ 0.023 \\ 456 \\ 0.023 \\ 456 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.034 \\ 0.023 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034 \\ 0.034$ | 555555555666666667777777778888888888889999999999 | $\begin{array}{c} 555555555555555555555555555555555555$ |    |

Table 1 Regults of experiment 1

# Alexandria Engineering Journal

April 1988

64

Alexandria Engineering Journal

M.R.M. Rizk, A. Khalifa and A.A. Abo Ouf

Figure 4

Figure 5

Alexandria Engineering Journal

April 1988

67