# DEVELOPMENT SYSTEM FOR THE TM32010 DSP BASED ON ZX-SPECTRUM MICROCOMPUTER

Ibrahim El-Abd, Mazhar B. Tayel and M. Galal A. Fahmy

Electrical Engineering Department, Faculty of Engineering, Alexandria University, Alexandria, Egypt

## ABSTRACT

In designing a device or a system based on a digital signal processor (DSP), the designer has to design the program that executes the intended functions, and to implement it by the DSP. This needs a development supporting tool by which the designer can control and monitor the performance of his device, and makes any necessary corrections or modifications. Although manufactures of DSP, render many facilities and development supporting tools, yet, they are difficult to obtain, expensive, special purpose, need training, and use relatively expensive host computers. This paper presents a development system for the TMS32010 DSP, which is the first member of the TMS320 DSPs family. The introduced system works under the control of "ZX-Spectrum" microcomputer, which is one the most simple, low-priced, and available microcomputers.

#### MTRODUCTION

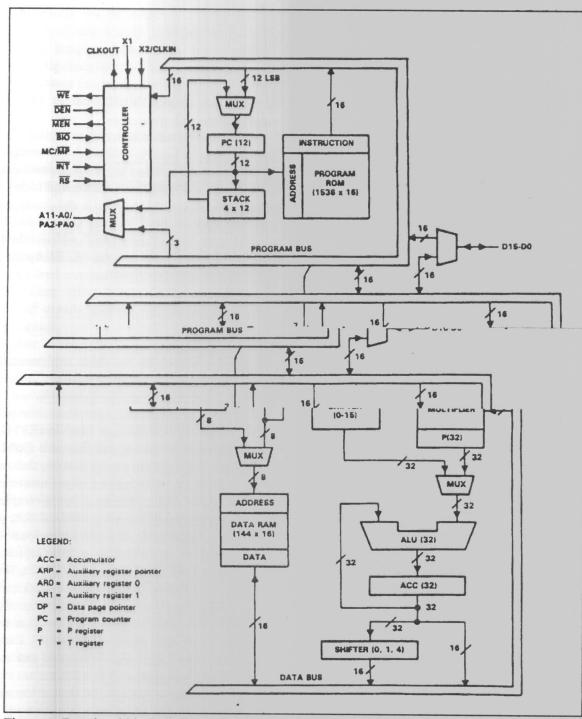

The TMS 320 digital single processing family is designed to support a wide range of high-speed or numericintensive application. The TMS 320 10 is the first member of this family. Figure (1) shows the functional block diagram of the TMS 320 10. This 16/32-bit single-chip microcomputer combines the flexibility of a high-speed controller with the numerical capability of an array processor thereby offering an inexpensive alternative to multichip bit-slice processors. The TMS 320 family untains the first MOS microcomputers capable of executing better than 6 million instructions per second. This high throughput is the result of the efficient and easily programmed instruction set and of the highly pelined architecture. Special instructions have been incorporated to speed the execution of digital signal processing (DSP) algorithms.

DEVELOPMENT SYSTEM AND SOFTWARE SUPPORT

Texas Instruments offers concentrated

development support for designing a TMS 32010-based microprocessor system. When developing an application, tools are provided to evaluate the performance of the

processor, to develop the algorithm implementation, and to fully integrate the design's software and hardware modules.

Sophisticated development operations are performed with the TMS 32010 Evaluation Module (EVM), Macro Assembler/Linker, Simulator, and Emulator (XDS). In the initial phase of developing an application, the evaluation module is used to characterize the performance of the TMS 32010. Once this evaluation phase is completed, the macro assembler and linker are used to translate program modules into object code and link them together. This puts the program modules into a form which can be loaded into the TMS 32010 Evaluation Module, Simulator, or Emulator. The simulator provides a quick means for initially debugging TMS 32010 software while the emulator provides real-time in-circuit emulation necessary to perform system level debug efficiently [1].

A complete list of TMS 32010 software and hardware development tools is given in Table (1).

Studying the construction and the instruction set of the TMS 32010, reveals the following points of view:

1- Although the instruction set is very versatile, yet, it is quite simple and small, such that assembly language programs can be easily converted manually to a m/c code without the need to an assembler.

Figure 1. Functional block diagram of TMS32010 DSP.

Table 1. TMS 32010 software and hardware support.

| Host Computer                | Operating System  | Part Number    |

|------------------------------|-------------------|----------------|

| DEC VAX                      | VMS               | TMDS3240210-08 |

| DEC VAX                      | Berkeley UNIX 4.1 | TMDS3240220-08 |

| IBM                          | MVS               | TMDS3240310-08 |

| IBM                          | CMS               | TMDS3240320-08 |

| TI/IBM PC                    | MS/PC-DOC         | TMDS3240810-02 |

|                              | SIMULATOR         |                |

| DEC VAX                      | VMS               | TMDS3240211-08 |

| TI/BM PC                     | MS/PC-DOS         | TMDS3240811-02 |

|                              | HARDWARE          |                |

| Evaluation Moudule(EVM)      |                   | RTC/EVM320A-03 |

| Analog Interface Board (AIB) |                   | RTC/EVM320C-06 |

| Emulator (XDS/22)            |                   | TMDS326210     |

| sun and rains                |                   |                |

2- If the hardware and the software of the system enables the host computer to receive and store a real time

input sequence, such that the computer can execute the algorithm under development by a non-real time BASIC program. and store the output sequence, such that the host computer can transmit it to the outside world at same input rate, than this will be equivalent (to some extent) to real-time in-circuit emulation. Clearly this arrangment is useful when the input sequence is independent of the output sequence.

- 3- If the system has the facility to control the operation of the DSP, such that the DSP executes the program using the stored input sequence while the output(or intermediate) sequence is monitored and stored in the host computer, then this arrangement will enable the user to check any part of his program, simply, by repeating the execution of the program using the same input sequence while monitoring any intermediate sequence. Actually this facility eliminates the need of a simulator.

- 4 Excluding the assembler and the simulator from the software (points 1 and 3) allows the use of simpler host computer.

Based on these introduced points of view, the Zx-

Spectrum microcomputer is selected as a host computer for the entened development system [2].

## SYSTEM DESCRIPTION

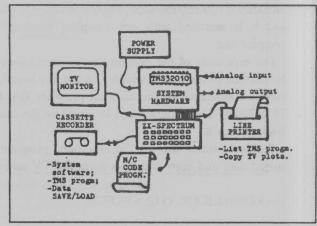

Figure (2) shows the lay out of the introduced development system. It is consisting of the Zx-Spectrum microcomputer, the mother board of the hardware, power supply, TV monitor audio cassette recorder, and line printer.

The hardware part accepts analog input

Figure 2. Lay out of the development system.

| Loc. | Lab.                     | Mnemonic<br>B Start | Comments Branch to STAQRT       |

|------|--------------------------|---------------------|---------------------------------|

| 0    | AUTO NEW TOTAL PROPERTY. |                     |                                 |

| 1    | Harmonia de la Cala      | B RUN               | Branch to RUN                   |

| 3    |                          |                     |                                 |

| 4    | START                    | Instructions        |                                 |

|      |                          | that set            |                                 |

|      |                          | initial             |                                 |

|      |                          | values, and         |                                 |

|      |                          | read constants      |                                 |

|      |                          |                     |                                 |

| n    |                          | B INT               |                                 |

| n+1  | RUN                      |                     |                                 |

| n+2  |                          | Program             |                                 |

|      |                          | Instructions        |                                 |

|      |                          |                     | Branch to INT                   |

|      | INT                      |                     |                                 |

|      | WAIT                     |                     | Total execution time must be le |

|      |                          |                     | than time between samples.      |

|      |                          |                     | C 11 INTO                       |

|      |                          | EINT                | Enable INT                      |

|      |                          | B WAIT              | Donal to WAIT                   |

|      |                          |                     | Branch to WAIT.                 |

signal of maximum amplitude 10 mv where it is to be band limited to (200-3400 c/s), sampled at a rate of (8 or 32)K sample/ s and stored in the host computer for subsequent digital signal processing.

The software that controls and monitors the operation of the system is to be loaded from a cassette recorder. The introduced control/monitor program is called "CMDSP"[3] and it is matched with any sampling rate up to 40K sample/ sec.

The m/c code of the program under development is to be entered to the host computer by the key board, then it can be transferred to the external program RAM of the TMS 32010. This program can be saved on the cassette or loaded from it.

The line printer can list the developed program or any stored data and copy any plots from the TV screen.

# HARDWARE OF THE SYSTEM

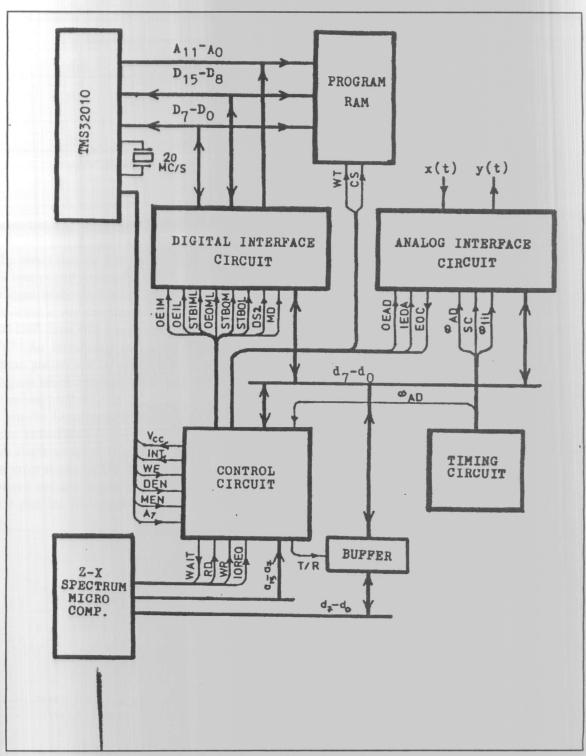

Figure (3) shows the block diagram of the introduced

hardware, it is mainly consisting of the following items

- Digital interface circuit;

- Analog interface circuit;

- Program RAM;

- Timing circuit;

- Control circuit;

- The TMS 32010 DSP.

# RECOMMENDATIONS FOR PROGRAMS TO BE DEVELOPED

Any program to be developed by the introduced systemust be designed in such a manner that it can respond to the INT input in proper time. The suggested form for an program is shown above:

When the DSP sences INT it branches to location? then to location "RUN" and begins to execute the programusing new input sample.

Figure 3. The block diagram for the hardware of introduced development system.

# \*\*\* Multiply By -0.7 \*\*\*

| Loc. |       |         | Mnemonic      | Comments                                    |

|------|-------|---------|---------------|---------------------------------------------|

|      | Lab.  | Code    | uiomomo       | Comments                                    |

| 000  | Lau.  | Code    | B START       | 植育美                                         |

| 1    |       | 249,0   |               |                                             |

| 2    |       | 0,4     | B RUN         |                                             |

| 3    |       | 249,0   |               | Load Acc. by 255.                           |

| 4    | START | 0,10    |               | SACL MSK (ACC) $\rightarrow_L$ MSK.         |

| 5    |       | 126,255 | LACK 255      | 128 → (ACC).                                |

| 6    |       | 80,2    | SACL MSK      | $(ACC)_1 \rightarrow XN.$                   |

| 7    |       | 126,128 | LACK 128      |                                             |

| 8    |       | 80,3    | SACL XN       |                                             |

| 8    | 1 700 | 249,0   | B IMT         | No. op. to give sufficient                  |

| 9    |       | 0,33    |               | time for the ZX Spectrum                    |

| 10   | RUN   | 127,128 | NOP           | to latch x(n) into the                      |

| 11   |       | 127,128 | NOP           | M.S. byte output latch.                     |

| 12   |       | 127,128 | NOP           |                                             |

| 13   |       | 127,128 | NOP           |                                             |

| 14   |       | 127,128 | NOP           | IN X, PAO $X = x(n)(NBC)*2^8$ .             |

| 15   |       | 127,128 | NOP           | LAC X,8 $x(n)^{*}2^{8} \rightarrow (ACC)$ . |

| 16   |       | 64,0    | IN X, PAO     | SACH X                                      |

| 17   |       | 40,0    | LAC X,8       | $(ACC)_H \rightarrow X = x(n)(NBC).$        |

| 18   |       | 88,0    | SACH X        | LAC X $X \rightarrow (ACC)$                 |

| 18   |       | 32,0    | LAC X         | Suppress sign extention.                    |

| 20   |       | 121,2   | AND MSK       | SUB XN $(ACC) = x(n)(TCC)$ .                |

| 21   | 1100  | 16,3    | SUB XN        | SACL X $(ACC)_L \rightarrow X$              |

| 22   |       | 80,0    | SACL X        | (T) = x(n).                                 |

| 23   |       | 106,0   | LT XMPYK 5325 | $K = -0.7*2^{12}$                           |

| 24   |       | 148,205 | PAC           | (Y) = -0.7* x(n) (TCC).                     |

| 25   |       | 127,142 | SACH Y,4      |                                             |

| 26   |       | 92,1    | LAC Y         | (ACC) = y(n) (NBC).                         |

| 27   |       | 32,1    | ADD XN        |                                             |

| 28   |       | 0,3     | SACL Y        |                                             |

| 29   |       | 80,1    | LAC Y,8       | $(Y) = y(n) *2^{8} (NBC).$                  |

| 30   |       | 40,1    | SACL Y        | M.S.byte input latch                        |

| 31   |       | 80,1    | OUT Y, PAO    | will contain y(n) (NBC).                    |

| 32   |       | 72,1    |               |                                             |

| ***  |       |         | EINT          | Wait for interrupt.                         |

| 33   | INT   | 127,130 | B WAIT        |                                             |

| 34   | WAIT  | 249,0   |               |                                             |

| 35   |       | 0,34    |               |                                             |

|      |       |         |               | 4                                           |

|      |       |         |               |                                             |

Table 6. Locations of the used quantities

| Symbol         | Symbol Quantity Description |                                                                                                      | 2Location |

|----------------|-----------------------------|------------------------------------------------------------------------------------------------------|-----------|

| X              | x(n)                        | Input sample                                                                                         | 22 0      |

| Y              | y(n)                        | output sample = $-0.7*x(n)$<br>= $-0.7*x(n)*2_{12}*2^4*2^{-16}$                                      | 1         |

| MSK            | 255                         | Mask                                                                                                 | 2 2       |

| x (n) from 0 < |                             | constant used to convert<br>$x (n) \text{ from } 0 \le x (n) \le 255$<br>to $-128 \le x (n) \le 127$ | 3         |

N.B. semble (ACC)<sub>H</sub> means bits 31 through 16 of the accumulator, and (ACC)L means bits 15 through 0.

It must be noted that the ZX Spectrum transmits x (n) to the M.S. byte output latch and receives y (n-1) from the M.S. byte input latch. Also x (n) and y(n) are stored in the Zx-Spectrum in normal binary code "NBC", while the TMS 32010 DSP deals with numbers in twos complement code "TCC". An introduced technique that takes into account these points, can be illustrated by the following simple program which obtains y (n) from multiplying x (n) by a constant, say -0.7.

Table (6) lists the locations of different quantities in data RAM of the TMS 32010.

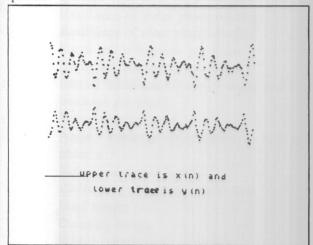

A speech single sampled at a rat of 8K sample/sec is used as an input sequence for the above program, where it was inverted and attenuated by a factor of 0.7. Figure (4) shows a plot for 256 samples from input and output sequences.

Figure 4. Result of "MULTIPLY BBY-0.7" program. (Sampling rate = 8 K sample/sec).

### CONCLUSION

This paper presents a development system for the TMS532010 DSP, the system is controlled by the "ZX-Spectrum" microcomputer, which is one of the most simple, low-priced and available microcomputers. The introduced system gives the user many facilities to correct his program during the development phase, and enables the user to execute his program by the TMS32010, in real-time, while monitoring its performance.

#### REFERENCES

- [1] TMS32010 User's Guide, Digital signal processor products, Texas Instru, emts, 1985.

- [2] Steven Vickers edited by Robin Bardbeer, "Sinclair ZX SPECTRUM BASIC programming, 1982.

- [3] Eng. M. Galal A. Fahmy; "Thesis submitted for the degree of Ph.D., 1990.